数字电路与逻辑设计之集成触发器的研发 从理论到实现的演进之路

在数字电路与逻辑设计的宏大体系中,集成触发器扮演着至关重要的角色,它不仅是构成时序逻辑电路的基本存储单元,更是现代数字系统,从微处理器到通信设备,实现复杂功能的核心基石。其研发历程,是一部融合了理论突破、工艺革新与设计智慧的技术演进史。

一、理论奠基:触发器的逻辑本质

触发器的研发始于对其逻辑功能的深刻理解。从最基本的RS触发器(置位-复位触发器)出发,研发人员明确了其具有两个稳定状态,能够存储1比特信息的核心特性。RS触发器存在禁止状态(R和S同时为1)的缺陷,这推动了更完善结构的探索。

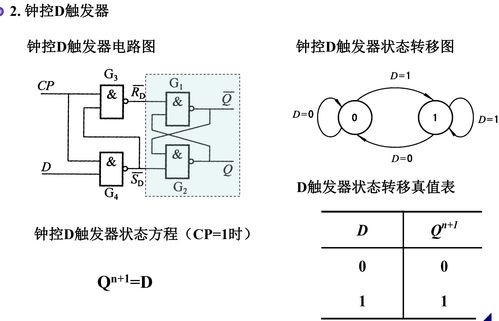

为消除不确定状态,并引入同步控制机制,时钟控制的电平触发型触发器(如同步RS触发器)被提出。但其在时钟有效期间对输入信号持续敏感的特性,容易导致“空翻”现象,在高速或复杂电路中可靠性不足。这一关键挑战,直接催生了边沿触发概念的诞生。

理论的重大飞跃体现在主从结构(Master-Slave)和边沿触发结构的提出。主从JK触发器通过两个级联的触发器,分别在时钟脉冲的上升和下降沿工作,有效解决了空翻问题,并具备了置位、复位、保持和翻转(Toggling)的完整功能。而利用门电路传输延迟实现的维持阻塞D触发器,则成为另一种高效、稳定的边沿触发方案,其“维持”与“阻塞”反馈通路的设计,是逻辑设计智慧的经典体现。这些理论模型为集成电路的实现提供了清晰的蓝图。

二、工艺实现:从分立到集成的飞跃

触发器的物理实现,紧密跟随半导体工艺的发展步伐。早期,触发器由分立的三极管、电阻、电容等元件在电路板上搭建而成,体积庞大、功耗高、可靠性差。

集成电路(IC)技术的出现,彻底改变了游戏规则。研发的核心任务转变为:如何在微小的硅片上,以极高的密度、可靠性和能效比,实现既定的触发器逻辑功能。这涉及到:

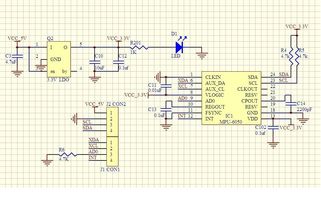

- 晶体管级设计:将逻辑门(如与非门、或非门)映射为CMOS(互补金属氧化物半导体)或TTL(晶体管-晶体管逻辑)等工艺下的晶体管网络。CMOS技术因其极低的静态功耗和良好的噪声容限,逐渐成为主流。研发人员需精细设计PMOS和NMOS管的尺寸比例,以优化速度、功耗和面积。

- 版图设计:将晶体管级的电路连接关系,转化为一系列几何图形(即版图),用于光刻制造。这要求研发工程师深谙工艺设计规则,在确保功能正确的前提下,尽可能压缩芯片面积,降低寄生参数,提升电路性能。

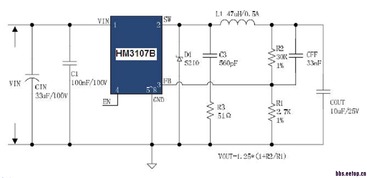

- 时序与功耗优化:在集成环境下,时钟信号的偏移(Skew)、数据的建立时间(Setup Time)和保持时间(Hold Time)变得极为关键。研发中需要借助EDA(电子设计自动化)工具进行精确的时序分析和验证。随着芯片规模扩大,动态功耗和泄漏功耗的控制成为研发重点,催生了时钟门控、电源门控等低功耗设计技术。

三、集成化与标准化:构建复杂系统的基石

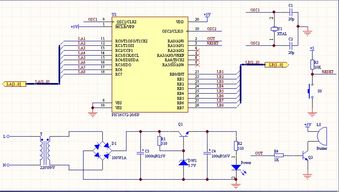

单一触发器的成功集成并非终点。研发的更高层次目标,是将触发器作为标准单元,大规模、模块化地应用于更复杂的时序系统中。

- 标准单元库:在ASIC(专用集成电路)和标准单元设计流程中,各种类型的触发器(D触发器、JK触发器、T触发器,带异步置位/复位端、使能端等不同配置)被设计、表征并纳入标准单元库。它们具有统一的电源轨、规整的物理尺寸和精确的时序/功耗模型,供系统设计者像搭积木一样调用。

- 寄存器与存储器阵列:将成千上万个触发器规则排列,并配以地址译码和读写控制电路,便构成了寄存器文件或静态随机存取存储器(SRAM)的核心存储阵列。这里的研发重点转向了高密度、低泄漏和高速访问技术。

- 可编程逻辑器件:在FPGA(现场可编程门阵列)中,其可编程逻辑单元(如查找表LUT)通常与一个或多个触发器紧密耦合。研发聚焦于如何设计灵活、高效的触发器与布线资源,以平衡灵活性、性能和面积。

四、前沿挑战与未来趋势

当今集成触发器的研发,已深入到纳米级工艺的复杂物理效应和系统级需求中:

- 变异性与可靠性:在先进工艺节点下,工艺波动、电压噪声和软错误对触发器存储状态的稳定性构成严峻挑战。研发方向包括采用更鲁棒的电路结构(如双互锁存储单元DICE)、误差检测与校正技术等。

- 近阈值与亚阈值计算:为追求极致能效,电路工作在接近或低于晶体管阈值电压的区域。这要求触发器在极低电压下仍能可靠工作,并忍受更大的时序波动,新型低电压触发器结构是研发热点。

- 与新型计算范式融合:在类脑计算、存内计算等新兴架构中,触发器的角色可能被重新定义或与新型非易失存储元件(如忆阻器)结合,研发范式正在发生深刻变革。

###

集成触发器的研发,是一条从抽象布尔逻辑到具体硅实现,再到支撑庞大数字帝国的持续创新之路。它不仅是电子工程技术的结晶,更是逻辑思维与物理实现完美结合的典范。随着工艺的不断微缩和应用需求的日益复杂,触发器的研发将继续在性能、功耗、可靠性和成本的多维边界上探索前行,为数字世界的每一次跃迁奠定坚实的基础。

如若转载,请注明出处:http://www.laike-cloud.com/product/44.html

更新时间:2026-04-16 03:26:16