集成电路版图设计与Cadence工具入门讲义

集成电路(IC)版图设计是连接电路设计与芯片制造的关键环节,它直接影响芯片的性能、面积和可靠性。本讲义以Cadence平台为例,系统性地介绍集成电路版图设计的基础知识、工具操作与研发实践。

一、集成电路版图设计概述

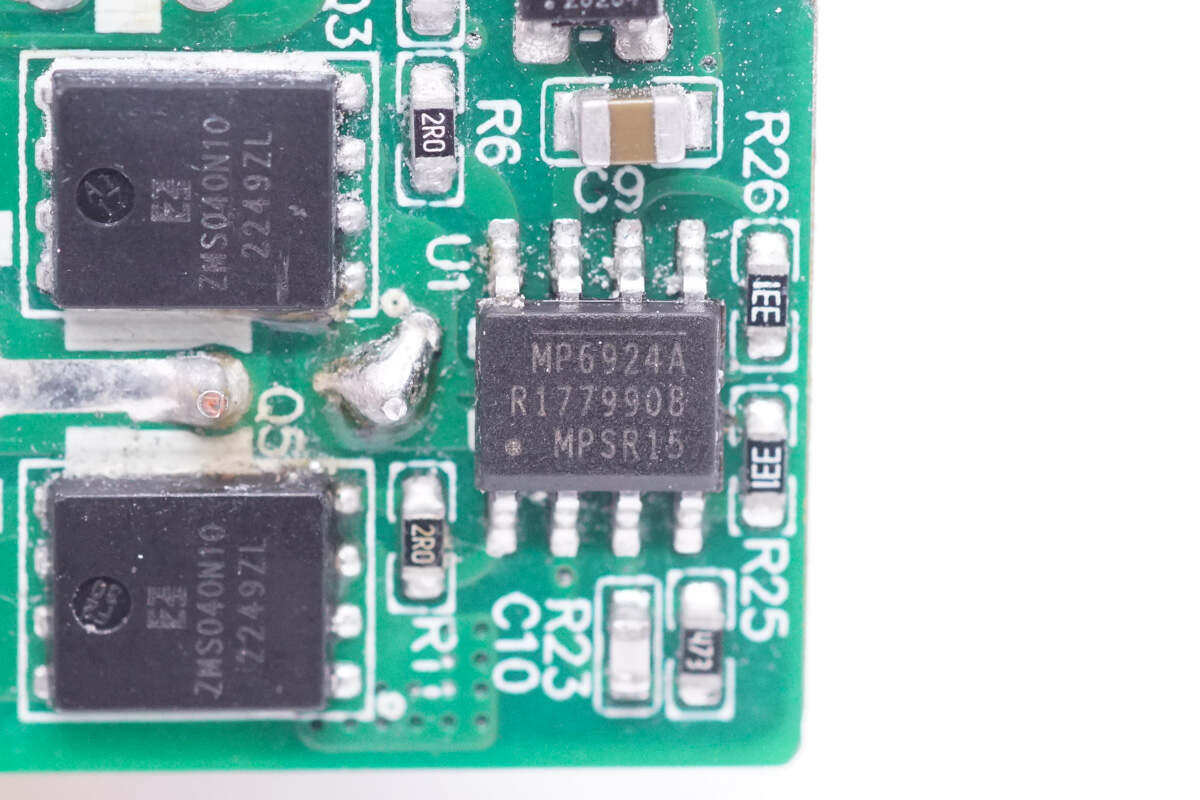

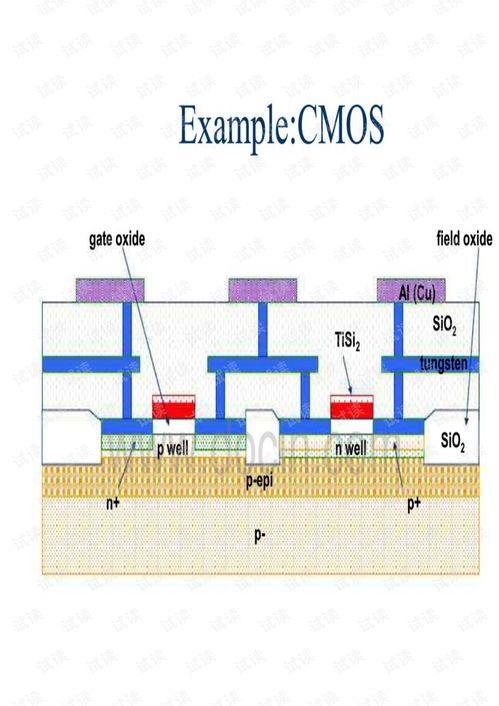

版图设计是将电路网表转化为一系列几何图形,这些图形定义了芯片制造过程中各层的物理结构。版图设计师需要深刻理解设计规则(Design Rules)、电气规则(Electrical Rules)以及工艺制程的约束。一个优秀的版图需要在满足所有规则的前提下,优化面积、功耗、信号完整性和可制造性。

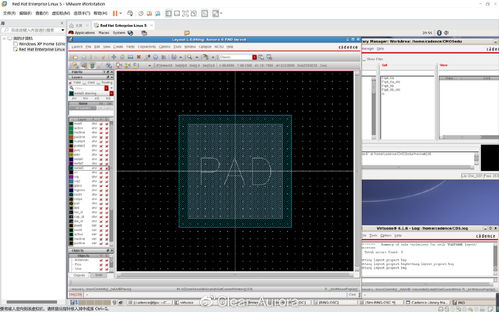

二、Cadence版图设计环境

Cadence Virtuoso是业界广泛采用的版图编辑工具。其环境主要包括:

- 库管理器(Library Manager):用于管理工艺库、设计库和单元。

- 版图编辑器(Layout Editor):核心设计窗口,提供丰富的图形绘制、编辑和验证功能。

- 属性编辑器(Property Editor):查看和修改设计对象的属性。

三、版图设计基础操作

- 创建单元与实例化:从基本图形(矩形、多边形等)开始构建晶体管、接触孔等基础元件,并将其组合成更复杂的单元(Cell),通过实例化(Instance)实现层次化设计。

- 图层与显示控制:熟悉工艺设计套件(PDK)提供的各层定义(如金属层、多晶硅层、扩散层等),并合理使用显示过滤器(Display Resource)提高设计可视性。

- 约束驱动设计:利用约束管理器设置线宽、间距等规则,确保设计符合规范。

四、版图验证与后仿真

设计完成的版图必须经过严格的验证:

- 设计规则检查(DRC):确保版图几何图形符合晶圆厂制定的制造规则。

- 电路图与版图一致性检查(LVS):验证版图实现的电路与原始电路网表在电气连接上完全一致。

- 寄生参数提取(PEX):提取版图中的寄生电阻和电容,并进行后仿真(Post-layout Simulation),以评估版图对电路性能(如速度、功耗)的实际影响。

五、研发实践与进阶技巧

在研发项目中,版图设计需与电路设计团队紧密协作:

- 匹配与对称性:对于差分对、电流镜等敏感电路,采用共质心、交叉耦合等版图技术以降低工艺偏差影响。

- 电源与地线规划:设计稳健的电源网络(Power Grid),确保电流密度均匀,避免电迁移(Electromigration)问题。

- 信号完整性:对于高频或敏感信号线,需考虑屏蔽、隔离和阻抗控制。

- 可制造性设计(DFM):采用添加冗余接触孔、天线效应避免等技巧,提升芯片制造的良率。

六、与资源

掌握Cadence版图设计工具是现代IC研发工程师的必备技能。建议读者结合本讲义,通过实际项目练习,并深入学习相关工艺文档、参考设计和在线社区(如EETOP等专业论坛)的讨论,不断积累经验。版图设计是艺术与工程的结合,唯有细心、耐心与创新,才能设计出高性能、高可靠的芯片。

如若转载,请注明出处:http://www.laike-cloud.com/product/38.html

更新时间:2026-04-16 10:29:28